(티니뉴스)

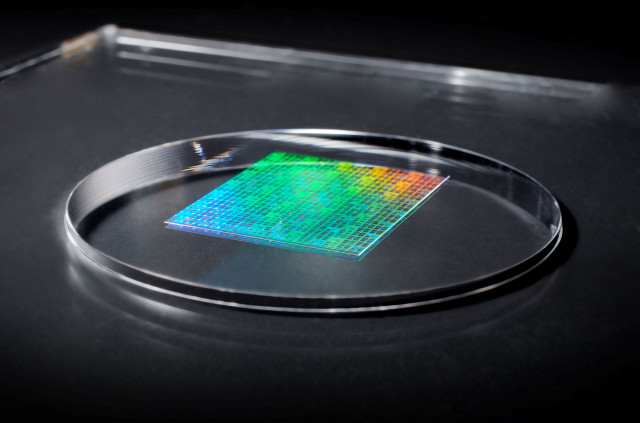

다이 닛폰 프린팅(Dai Nippon Printing Co., Ltd., DNP, 도쿄증권거래소: 7912)이 회로 선폭 10나노미터(nm, 1nm는 10⁻⁹m)의 나노임프린트 리소그래피(NIL) 템플릿 개발에 성공했다고 발표했다. 이 새로운 템플릿은 1.4nm 세대에 상응하는 로직 반도체의 패터닝을 가능하게 하며, 최첨단 로직 반도체의 소형화 요구를 충족한다.

배경 및 목표

최근 몇 년간 더 정교한 장치로의 전환에 따라 최첨단 반도체에서 훨씬 더 높은 소형화 요구가 발생했으며, 이는 극자외선(Extreme Ultra-Violet, EUV) 리소그래피 기반 생산의 발전을 이끌었다. 그러나 EUV 리소그래피는 생산 라인 구축과 노출 공정에서 상당한 자본 투자, 에너지 소비 및 운영 비용을 필요로 한다.

DNP는 2003년부터 NIL 템플릿을 개발해 왔으며, 고정밀 패터닝에 대한 광범위한 노하우를 성공적으로 축적했다.

이번 최신 개발에서 DNP는 10nm 선폭 패턴을 가진 NIL 템플릿을 개발했다. 이는 EUV 리소그래피 공정의 일부를 대체할 수 있으며, EUV 리소그래피 생산 공정이 없는 고객을 위해 최첨단 로직 반도체 제조를 용이하게 한다.

주요 특징

· DNP는 리소그래피 장치로 형성된 패턴에 박막 증착 및 식각을 통해 패턴 밀도를 두 배로 높이는 자가정렬 이중 패터닝(Self-Aligned Double Patterning, SADP)을 활용하여 회로 선폭 10nm의 새로운 NIL 템플릿을 성공적으로 달성했다.

· 이 기술은 또한 최첨단 반도체 제조의 노출 공정에서 전력 소비를 줄인다. NIL을 사용한 초미세 반도체용 에너지 절약형 처리 기술 덕분에 이제 아르곤 플루오라이드(ArF) 이머전 및 EUV와 같은 현재 사용 가능한 노출 공정의 약 10분의 1 수준으로 전력 소비를 절감하는 것이 가능해졌다.

향후 계획

DNP는 NIL 템플릿에 대한 평가 작업을 시작했으며, 2027년에 양산을 시작하는 것을 목표로 하고 있다. DNP는 NIL 템플릿의 추가 개발을 추진하고 증가하는 수요를 충족시키기 위해 생산 능력을 강화하여 2030회계연도에 NIL 관련 매출 40억엔 증가를 목표로 하고 있다.

세부 내용

다이 닛폰 프린팅(Dai Nippon Printing Co., Ltd., DNP, 도쿄증권거래소: 7912)이 회로 선폭 10나노미터(nm, 1nm는 10⁻⁹m)의 나노임프린트 리소그래피(NIL) 템플릿 개발에 성공했다고 발표했다. 이 새로운 템플릿은 1.4nm 세대에 상응하는 로직 반도체의 패터닝을 가능하게 하며, 최첨단 로직 반도체의 소형화 요구를 충족한다.

배경 및 목표

최근 몇 년간 더 정교한 장치로의 전환에 따라 최첨단 반도체에서 훨씬 더 높은 소형화 요구가 발생했으며, 이는 극자외선(Extreme Ultra-Violet, EUV) 리소그래피 기반 생산의 발전을 이끌었다. 그러나 EUV 리소그래피는 생산 라인 구축과 노출 공정에서 상당한 자본 투자, 에너지 소비 및 운영 비용을 필요로 한다.

DNP는 2003년부터 NIL 템플릿을 개발해 왔으며, 고정밀 패터닝에 대한 광범위한 노하우를 성공적으로 축적했다.

이번 최신 개발에서 DNP는 10nm 선폭 패턴을 가진 NIL 템플릿을 개발했다. 이는 EUV 리소그래피 공정의 일부를 대체할 수 있으며, EUV 리소그래피 생산 공정이 없는 고객을 위해 최첨단 로직 반도체 제조를 용이하게 한다.

주요 특징

· DNP는 리소그래피 장치로 형성된 패턴에 박막 증착 및 식각을 통해 패턴 밀도를 두 배로 높이는 자가정렬 이중 패터닝(Self-Aligned Double Patterning, SADP)을 활용하여 회로 선폭 10nm의 새로운 NIL 템플릿을 성공적으로 달성했다.

· 이 기술은 또한 최첨단 반도체 제조의 노출 공정에서 전력 소비를 줄인다. NIL을 사용한 초미세 반도체용 에너지 절약형 처리 기술 덕분에 이제 아르곤 플루오라이드(ArF) 이머전 및 EUV와 같은 현재 사용 가능한 노출 공정의 약 10분의 1 수준으로 전력 소비를 절감하는 것이 가능해졌다.

향후 계획

DNP는 NIL 템플릿에 대한 평가 작업을 시작했으며, 2027년에 양산을 시작하는 것을 목표로 하고 있다. DNP는 NIL 템플릿의 추가 개발을 추진하고 증가하는 수요를 충족시키기 위해 생산 능력을 강화하여 2030회계연도에 NIL 관련 매출 40억엔 증가를 목표로 하고 있다.

세부 내용